Fpga

-

Vivado Design Suite 2017.1: UX e Usabilità

Effectiveness, efficiency, satisfaction ISO 9241-11,1998 Le definizioni di usabilità date in letteratura dai ricercatori nel tentativo di chiarirne il significato sono numerose, ma quella che fa al caso nostro per la sua semplicità è quella proposta nello standard ISO 9241 come “l’efficacia (effectiveness), efficienza (efficiency) e soddisfazione (satisfaction) con i quali gli utenti raggiungono determinati…

-

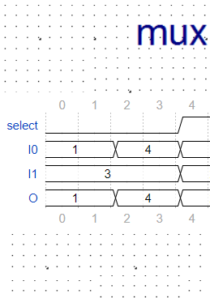

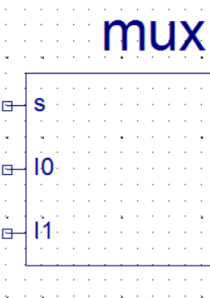

Getting started: Come scrivere un testbench con MyHDL?

Quando puoi misurare ciò di cui stai parlando, ed esprimerlo in numeri, tu conosci qualcosa su di esso; ma quando non puoi misurarlo, quando non puoi esprimerlo in numeri, la tua conoscenza è scarsa e insoddisfacente: può essere l’inizio della conoscenza, ma nei tuoi pensieri, sei avanzato poco sulla via della scienza. – William Thomson,…

-

Getting started: Test benching MyHDL con ISE Simulator

This phase is as important as the design phase, and as a general rule, the amount of time spent simulating should be about twice the design time. Gina R. Smith, FPGA designer Un sistema descritto in VHDL viene solitamente simulato per analizzarne il comportamento, stimolando i possibili ingressi e verificando se i segnali in uscita sono quelli…

-

MyHDL: a Python-Based HDL

Con l’affermarsi del movimento dei makers abbiamo assisitito al diffondersi di piattaforme embedded (ARM), che prima erano ad appannaggio dei soli specialisti, presso un pubblico più vasto composto da hobbisti e persone non del settore. Questo cambiamento ha portato alla ribalta linguaggi di programmazione ad alto livello come Python che è noto per la sua…

-

Getting Started: FPGAs Hello World!

L’intento di questo articolo non é di fornire una guida al VHDL, ma un workflow dallo schematico al bitstream attraverso l’ISE Design Suite di Xilinx rispondendo alle domande di chi compra un nuovo FPGA e non sa da dove iniziare. Registratevi al sito Xilinx e createvi un account e scaricate Xilinx ISE Design Suite per…

-

Getting started: Design di un Perceptron in FPGA con Vivado

In questo articolo per la rivista Elettronica Open Source avevamo già visto sia la teoria sia la pratica su come realizzare un modello con Simulink (Matlab) e System Generator di una semplice rete neurale artificiale (ANN) perceptron e come eseguirne l’addestramento con NNTOOL. Seguendo un procedimento analogo possiamo implementare il nostro perceptron su un FPGA. Tech…

-

Ciò che l’occhio della rana comunica al cervello della rana: da Kant alle reti neurali artificiali

Il seguente articolo teorico fa parte di un progetto didattico , nato in modo informale da circa un anno presso l’ Istituto Superiore Serale “G.Giorgi- Fermi” (Treviso), impegnato nella modellazione ed implementazione su singolo chip FPGA di reti neurali. Il nostro intento è di rendere questo progetto ufficiale e, di ampliare così l’offerta formativa dell’istituto.…